集成电路设计实践 从运放设计入门到精通

集成电路设计是现代电子技术的核心领域之一,其中运算放大器(Operational Amplifier,简称运放)的设计更是模拟集成电路设计的基石。无论是初学者还是经验丰富的工程师,掌握运放设计的原理与实践都是提升集成电路设计能力的关键。

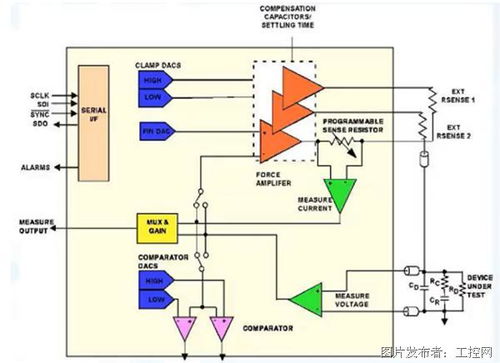

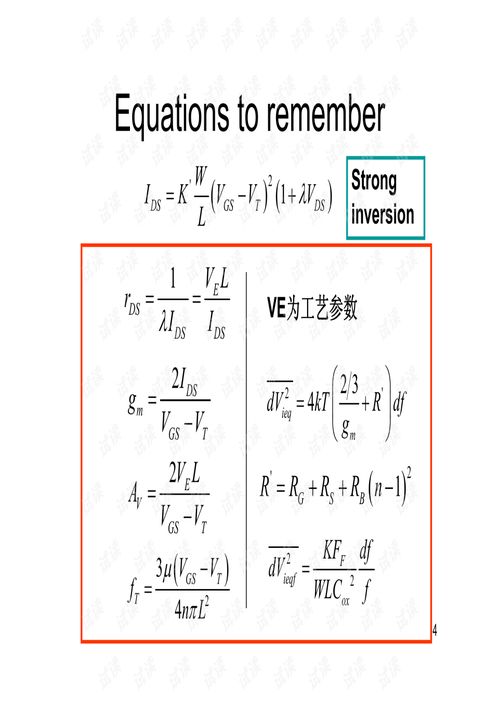

运放作为一种高增益、差分输入、单端输出的电压放大器,其性能直接影响到整个模拟系统的精度、带宽、功耗和稳定性。一个优秀的运放设计,需要在增益、带宽、压摆率、噪声、失调电压、共模抑制比、电源抑制比等多个性能指标之间取得精妙的平衡。

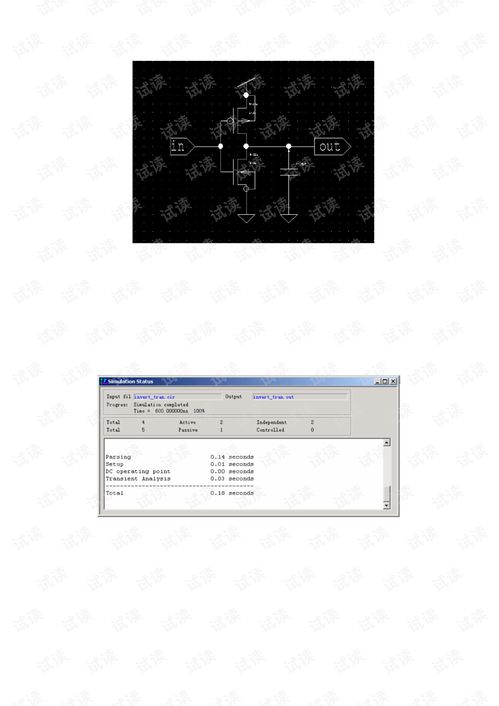

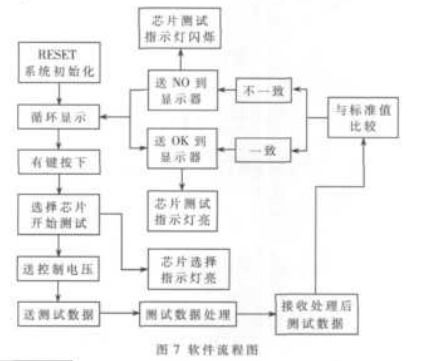

在集成电路设计实践中,运放设计通常遵循从架构选择到晶体管级实现,再到版图设计与后仿真的完整流程。初学者可以从最基本的五管差分对套筒式运放入手,理解偏置电路、差分输入对、负载和输出级的工作原理。随着设计的深入,会逐渐接触到折叠式共源共栅、两级运放、增益自举等更复杂的结构,以满足更高性能指标的要求。

设计过程中,EDA工具(如Cadence Virtuoso)的使用至关重要。设计师需要通过仿真反复验证设计的DC工作点、AC频率响应、瞬态响应以及工艺角(Corner)和蒙特卡洛(Monte Carlo)分析,以确保芯片在制造工艺波动下仍能稳定工作。版图设计阶段则需要充分考虑匹配、寄生效应、天线效应、闩锁效应等问题,好的版图是电路性能在硅片上得以实现的有力保障。

对于资源编号为“901602518.pdf”这类具体的参考资料,它很可能是一份详尽的讲义或实验手册,系统性地引导学习者完成一个完整的运放设计项目。通过研习此类资料,并结合实际的仿真与设计练习,工程师能够将抽象的理论知识转化为解决实际工程问题的能力。

集成电路设计,尤其是运放设计,是一门理论与实践紧密结合的学科。它要求设计师不仅要有扎实的电路理论功底,还要熟悉半导体工艺、EDA工具和严谨的设计流程。在这个信息爆炸的时代,善于利用如“eetop.cn”这样的专业论坛和丰富的网络资源(包括各类PDF教程),进行系统性的学习和持续的实践,是每一位IC设计者成长道路上不可或缺的一环。从理解一个晶体管开始,到设计出一个高性能的运放,再到最终流片验证,这个过程充满了挑战,也蕴含着无尽的创新乐趣与职业成就感。

如若转载,请注明出处:http://www.jabouyo.com/product/56.html

更新时间:2026-04-18 05:40:43