硬件与软件协同驱动的集成电路设计 从综合到功能仿真的全流程解析

集成电路(IC)设计是电子工业的基石,其复杂性与日俱增。现代IC设计已不再是简单的硬件布局,而是硬件与软件深度协同的系统工程。这一过程通常涵盖设计、综合、功能仿真等关键阶段,每个环节都离不开硬件描述语言(HDL)与专用软件工具的紧密配合。本文将系统阐述硬件与软件如何共同完成从概念到功能验证的集成电路设计全流程。

一、 设计输入:硬件描述语言的桥梁作用

设计的起点是设计输入。工程师使用硬件描述语言(HDL),如VHDL或Verilog,以文本形式描述电路的功能、行为和结构。这本质上是软件行为:工程师像编写程序一样,利用高级抽象来描述寄存器传输级(RTL)设计。此时的代码定义了电路的“行为”规范,是后续所有硬件实现的基础。软件工具(如文本编辑器、语法检查器)在此阶段提供支持。

二、 逻辑综合:软件将行为转化为门级网表

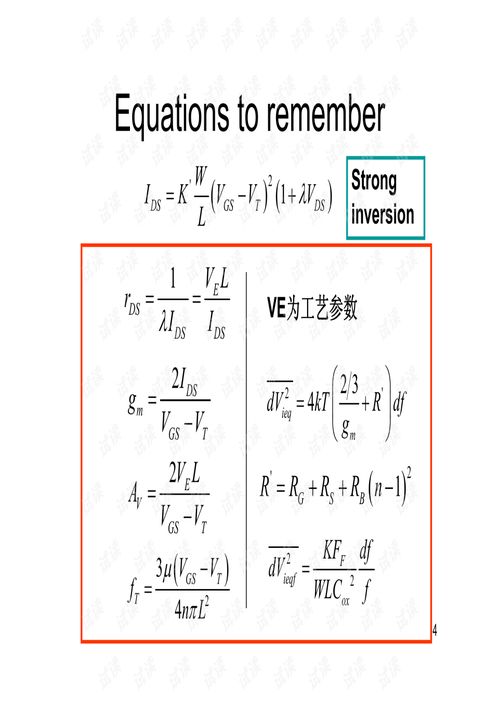

逻辑综合是硬件与软件协同的核心环节之一。设计师使用综合软件(如Synopsys Design Compiler、Cadence Genus)将RTL级的行为描述,转换(“综合”)为基于目标工艺库(如台积电7nm库)的门级网表。这个过程是自动化的:

- 软件解析RTL代码,理解其逻辑功能。

- 软件根据时序、面积、功耗等约束,从工艺库中选取合适的标准单元(如与门、或门、触发器等)进行映射和优化。

- 输出一个门级网表,这是一个由标准单元及其连接关系构成的、可用于制造的硬件电路描述。

综合是“软”指令(RTL代码和约束)通过复杂算法,生成“硬”结构(网表)的典型过程,充分体现了软件对硬件实现的决定性指导作用。

三、 功能仿真:软件构建的虚拟测试环境

在设计的任何阶段,尤其是在RTL设计和综合之后,都必须进行功能仿真以验证设计的正确性。这是纯软件层面的工作,但模拟的是硬件行为。

- 仿真器软件(如Mentor Graphics的ModelSim、Cadence的Xcelium)读取HDL代码或门级网表。

- 工程师编写测试平台(Testbench),这也是用HDL编写的软件程序,用于生成各种输入激励信号,并监测输出响应。

- 仿真器在计算机中建立一个虚拟的电路模型,按照测试平台的激励运行,并计算出电路的输出波形和内部信号变化。

- 工程师通过分析波形和日志,验证电路功能是否符合预期,发现并修复逻辑错误。

功能仿真器就像一个完全由软件构建的“虚拟实验室”,允许在设计物理硬件之前,以极低的成本和时间对复杂设计进行反复测试和调试。

四、 前后端协同与最终验证

在综合生成门级网表后,设计进入物理实现阶段(布局布线),这同样由专用EDA软件完成。即使在这一“硬”实现阶段,软件也持续发挥作用:

- 形式验证软件:数学上等价性检查,确保综合前后的网表功能一致,避免综合引入错误。

- 时序仿真:在布局布线后,加入实际走线延迟信息进行仿真,更精确地验证电路在真实时序下的功能。

- 硬件辅助仿真与原型验证:对于超大规模设计,会使用FPGA原型验证平台。这需要将设计编译到FPGA上,这本身是一个软件综合与布局布线过程。FPGA硬件运行起来后,其速度远快于软件仿真,可以运行真实的软件栈进行系统级验证,实现了“硬件”原型与“软件”测试环境的深度融合。

结论

集成电路设计是一个典型的“软硬结合”的典范。硬件(最终实现的芯片)是目标和载体,而软件(HDL、EDA工具链、测试平台)是整个设计过程的灵魂、工具和方法论。从行为描述、逻辑综合到功能仿真,软件不仅定义了硬件的功能,还自动化地完成了从抽象到物理实现的转换,并构建了全面的虚拟验证环境。正是这种深度的协同,使得设计数亿乃至上百亿晶体管的复杂SoC成为可能,持续推动着信息技术的飞速发展。

如若转载,请注明出处:http://www.jabouyo.com/product/71.html

更新时间:2026-04-08 05:39:21