深度报告 | 芯片设计EDA 2.0时代 三大路径破解六大挑战

随着集成电路设计复杂度的指数级增长和工艺节点的持续演进,传统电子设计自动化(EDA)工具与方法学正面临前所未有的压力。一个被称为“EDA 2.0”的新时代已经拉开帷幕,其核心在于通过智能化、云端化与系统化协同,赋能设计者应对后摩尔定律时代的严峻挑战。本报告将深入剖析当前芯片设计面临的六大核心挑战,并解读引领产业变革的三大关键路径。

第一部分:芯片设计面临的六大时代挑战

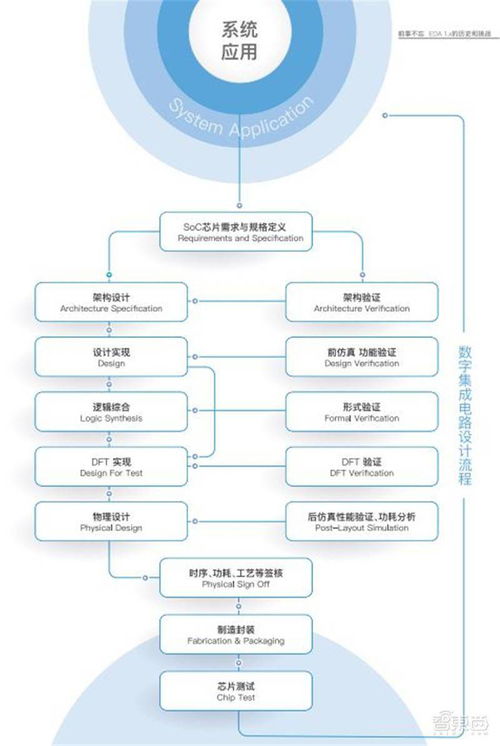

- 设计复杂度爆炸: 芯片规模已达数百亿晶体管,集成IP种类繁多,软硬件协同设计、系统级验证的复杂度呈非线性攀升,传统设计流程效率瓶颈凸显。

- 物理与工艺壁垒高企: 先进工艺(如3nm及以下)带来的物理效应(如量子隧穿、寄生效应)愈发显著,设计与制造(DTCO)的协同需求空前强烈,对EDA工具的精度和预测能力提出极致要求。

- 研发成本与周期失控: 尖端芯片的研发投入动辄数亿美元,设计、验证、流片周期漫长,任何迭代失误都可能导致巨大的经济与时间损失,市场窗口转瞬即逝。

- 人才短缺与知识断层: 具备尖端节点设计经验的专业工程师稀缺,设计方法论与工具使用门槛高,企业面临严重的人才瓶颈与知识传承困境。

- 系统级与多物理场优化需求: 芯片已演变为“系统级芯片”(SoC),需统筹考虑性能、功耗、面积(PPA)、信号完整性、热管理、可靠性等多维度、多物理场的联合优化。

- 数据孤岛与工具碎片化: 设计各阶段数据格式不一,工具链协同不畅,数据与知识无法在流程中有效流动和复用,形成效率黑洞。

第二部分:迈向EDA 2.0的三大核心路径

为系统性破解上述挑战,产业界正沿着三大路径推动EDA向2.0阶段演进:

路径一:AI驱动的智能设计

这是EDA 2.0最显著的标志。通过引入机器学习(ML)、深度学习(DL)等技术,将AI深度融合于设计全流程:

- 智能辅助与自动化: 在布局布线、逻辑综合、验证等环节,AI可大幅提升效率与结果质量,如自动生成测试向量、优化布局、预测设计热点。

- 设计空间探索(DSE): AI能快速遍历海量设计参数组合,寻找PPA最优解,将传统需数周的手动探索压缩至数小时。

- 知识沉淀与复用: 学习历史成功设计数据,形成可复用的设计策略与IP,降低对个别专家经验的依赖,赋能普通设计团队。

路径二:云原生与平台化协同

突破本地计算资源与协同模式的限制:

- 云端弹性算力: 将计算密集型的仿真、验证、物理实现等任务迁移至云端,利用弹性可扩展的算力池,大幅缩短任务周期。

- 统一数据与平台: 构建云原生的统一设计平台,打通从架构探索、前端设计、后端实现到签核的全流程数据链,实现工具无缝协同与数据的实时共享。

- 协作新模式: 支持全球分布团队实时在线协同设计,并促进EDA厂商、设计公司、晶圆厂、IP供应商在安全可信环境下的紧密协作。

路径三:系统级与多维融合设计

从“芯片设计”升维至“系统设计”:

- 电子系统级(ESL)与数字孪生: 在更高抽象层级进行系统架构探索与性能建模,结合数字孪生技术,实现软硬件并行开发与早期验证。

- 多物理场、多尺度仿真融合: 集成电、热、力、电磁等多物理场分析工具,在芯片设计早期评估并优化可靠性、散热及信号完整性等问题。

- Chiplet与异构集成设计支持: 提供面向Chiplet(芯粒)的先进封装协同设计、互连分析与系统级验证能力,支撑异构集成这一延续摩尔定律的关键路径。

与展望

EDA 2.0并非单一工具的升级,而是一场涵盖技术、平台与生态的范式革命。通过 “AI智能化” 提升设计自动化和决策水平,通过 “云平台化” 重构计算模式和协作流程,通过 “系统融合化” 拓展设计的边界与维度,三者交织并进,共同构成应对未来芯片设计挑战的基石。

对于集成电路设计企业而言,主动拥抱EDA 2.0趋势,重塑设计流程与方法学,将是在激烈技术竞争中获取差异化优势、控制成本与风险、最终赢得市场的关键。EDA工具将进一步演变为集智能引擎、协同平台与知识载体于一体的“芯片设计大脑”,持续推动集成电路产业向前沿纵深突破。

如若转载,请注明出处:http://www.jabouyo.com/product/55.html

更新时间:2026-04-18 17:58:37