超大规模集成电路设计中的MOS器件原理(三)与集成电路设计

超大规模集成电路(VLSI)设计是现代电子技术的核心,而金属氧化物半导体(MOS)器件作为其基本构建单元,其原理理解至关重要。本文是系列文章的第三部分,将深入探讨MOS器件原理及其在集成电路设计中的应用,涵盖器件特性、设计挑战以及实际优化策略。

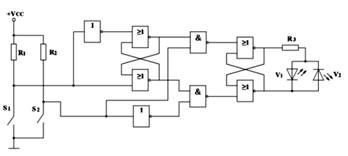

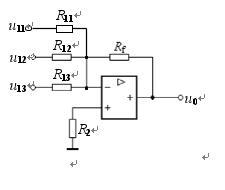

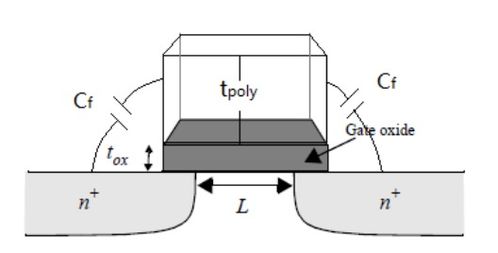

MOS器件的基本原理基于场效应晶体管(FET)结构,包括源极、漏极、栅极和衬底。当栅极施加电压时,会在半导体表面形成导电沟道,从而控制电流从源极流向漏极。这种开关行为是数字电路的基础,例如在逻辑门中实现二进制操作。在超大规模集成电路中,MOS器件的尺寸不断缩小,遵循摩尔定律,这带来了更高的集成度和性能,但也引入了短沟道效应、漏电流增加和功耗问题。因此,设计时必须考虑器件缩放极限,并采用多阈值电压技术或高介电常数材料来优化性能。

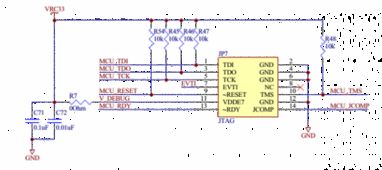

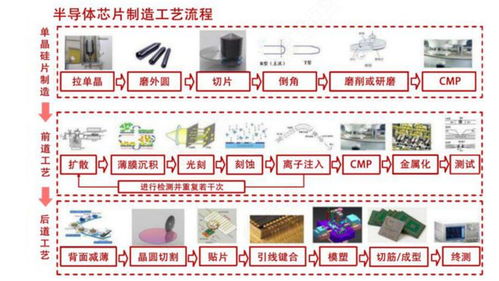

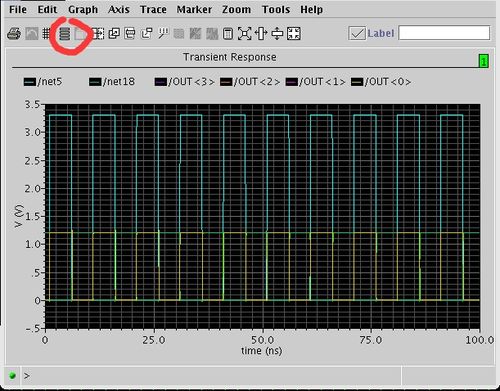

在集成电路设计中,MOS器件的原理直接应用于电路布局和时序分析。例如,在CMOS(互补MOS)技术中,结合NMOS和PMOS器件,可以实现低功耗和高噪声容限的逻辑电路。设计流程包括前端设计(如逻辑综合)和后端设计(如物理布局),其中MOS器件的参数(如阈值电压和跨导)会影响电路的速度和功耗。随着工艺节点向纳米级演进,设计者需应对寄生效应和热管理挑战,采用EDA工具进行仿真和验证。

掌握MOS器件原理是超大规模集成电路设计的关键,它不仅驱动了技术进步,还推动了从微处理器到存储芯片的广泛应用。随着新材料如FinFET和GAA晶体管的引入,设计者将继续优化器件性能,以满足人工智能和物联网等新兴领域的需求。

如若转载,请注明出处:http://www.jabouyo.com/product/27.html

更新时间:2026-04-16 02:37:54